# Motionpack FD Model 1 DESCRIPTIVE INFORMATION

YASKAWA MOTION CONTROLLER EXTENSION SYSTEM 1

#### INTRODUCTION

This Manual describes the functions and specifications of the Motionpack FD series model 1 (extension system 1).

The Motionpack FD series model 1 (extension system 1) is added with the builtin sequencer board (JAMP-S130) to the basic system model 0. The built-in sequencer and M-NET interface can be used in addition to the basic functions of the Motionpack FD series.

In this manual, M-NET interface and the built-in sequencer that is added to the model 1 is described.

For the funcions and specifications of the Motionpack FD series, refer to "Motionpack FD Series USER'S MANAUL" SIE-C883-1.1.

# CONTENTS

|                                             | Page                         |

|---------------------------------------------|------------------------------|

|                                             | Page                         |

|                                             | ······                       |

| 1. Motionpack FD SERIES MODEL 1 ·····       | ·                            |

| 1:1 SYSTEM CONFIGURATION ·····              | •                            |

| 1.2 SPECIFICATIONS OF MODEL 1 ·····         |                              |

| 1.3 MODEL 1 PARAMETER SETTING               |                              |

| 2. OUTLINE OF BUILT-IN SEQUENCER ······     |                              |

| 2.1 PERIPHERAL DEVICES                      |                              |

| 2.2 SPECIFICATIONS ······                   | ••••••7                      |

| 3. BEFORE USING BUILT-IN SEQUENCER ······   |                              |

| 3.1 TECHNICAL TERMS ······                  |                              |

| 3.2 BUILT-IN SEQUENCER SYSTEM CONFIGURATION |                              |

| 3.3 ADDRESS MAP ·····                       |                              |

| 3.4 RELATIONS BETWEEN I/O SIGNALS AND ADDRE | <b>SS</b> · · · · · · · · 15 |

| 4. BUILT-IN SEQUENCER INSTRUCTIONS          |                              |

| 5. EXPLANATIONS OF BUILT-IN SEQUENCER INST  | RUCTIONS 18                  |

| 5.1 RELAY INSTRUCTIONS                      |                              |

| 5.2 CONTROL INSTRUCTIONS                    |                              |

| 5.3 TIMER AND COUNTER INSTRUCTIONS          |                              |

| 5.4 REGISTER INSTRUCTIONS                   |                              |

| 6. LOGIC PROGRAM EDITING ······             |                              |

| 6.1 LOGIC PROGRAM EDITING                   |                              |

| 6.2 FORMAT OF ORIGINAL LADDER FILE ······   |                              |

| 6.3 FORMAT OF LIST FORMAT FILE              |                              |

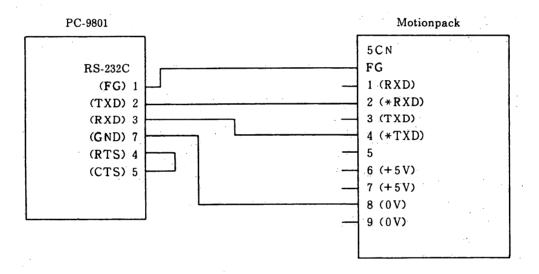

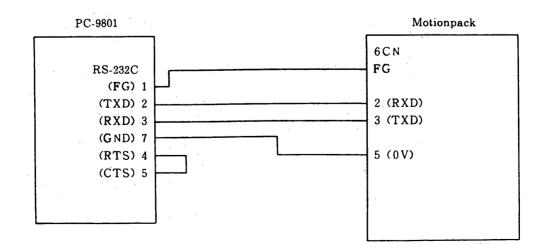

| 6.4 CONNECTION WITH PERSONAL COMPUTER ····  |                              |

| 7. CHECKING LOGIC ·····                     |                              |

| 7.1 CHECKING LOGIC PROGRAM SYNTAX           |                              |

# CONTENTS (Cont'd)

| CONTENTS (Cont'd)                                    |          |

|------------------------------------------------------|----------|

|                                                      | Page     |

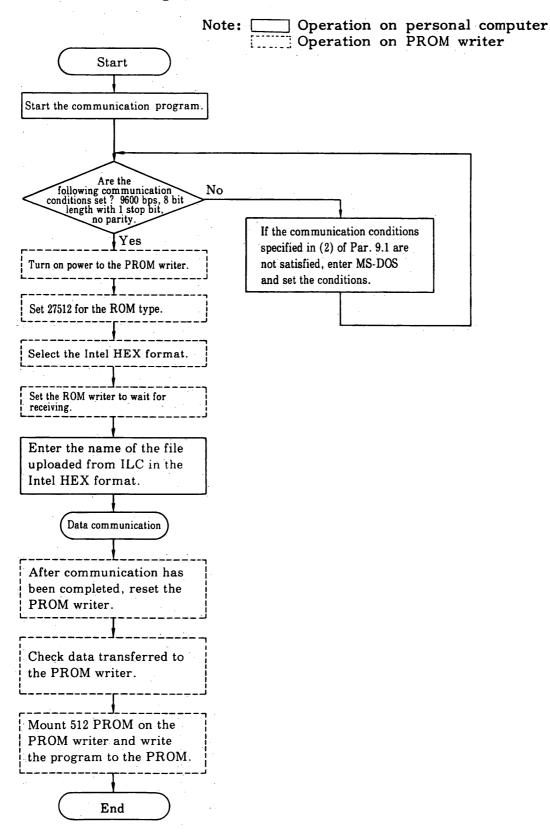

| 8. STORING LOGIC PROGRAM IN ROM ·····                | -        |

| 8.1 CONNECTING TO PROM WRITER ·····                  | • •      |

| 8.2 PROCEDURE FOR STORING LOGIC PROGRAM INTO ROM     |          |

| 9. FIXED I/O SIGNALS ·····                           |          |

| 9.1 FIXED INPUT SIGNALS ·····                        |          |

| 9.2 FIXED OUTPUT SIGNALS ·····                       |          |

| 10. EXTERNAL DATA SETTING AND INTERNAL DATA READ-OUT |          |

| 10.1 SIGNALS ·····                                   | 56       |

| 10.2 I/O MAP (INTERNALLY-FIXED ADDRESS) ·····        |          |

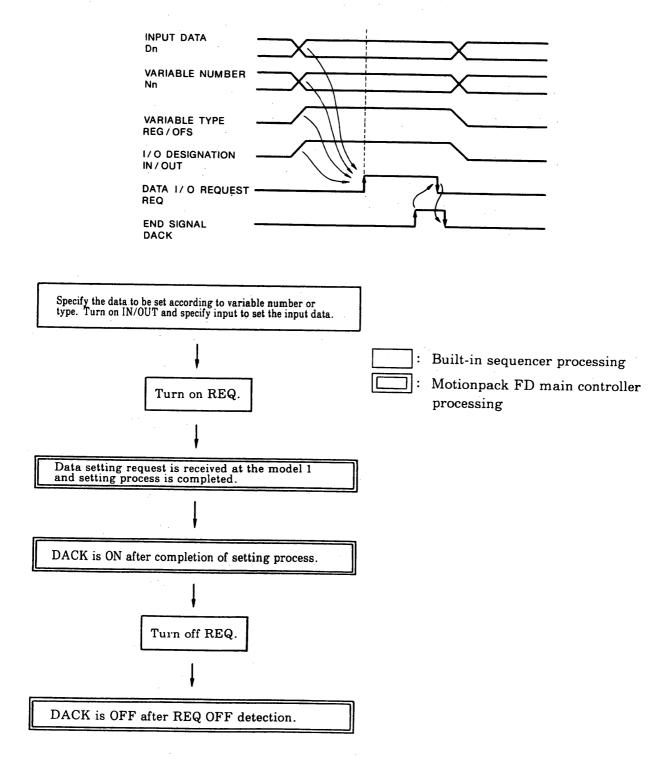

| 10.3 EXTERNAL DATA SETTING SEQUENCE ·····            |          |

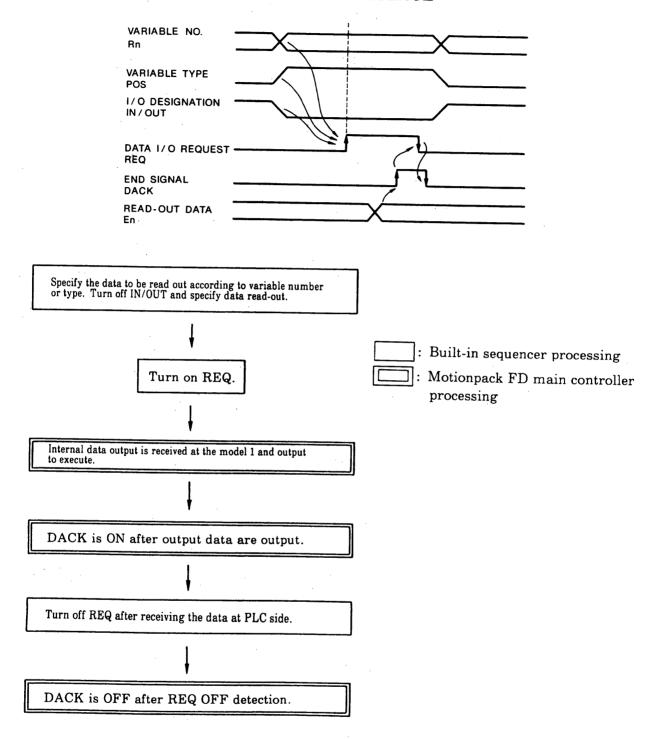

| 10.4 INTERNAL DATA READ-OUT SEQUENCE ·····           |          |

| 11. EXTERNAL COMPENSATION ·····                      | · ·      |

| 11.1 SPECIFICATIONS OF COMPENSATION DATA             |          |

| 11.2 ABSOLUTE VALUE COMPENSATION ·····               |          |

| 11.3 INCREMENTAL VALUE COMPENSATION                  |          |

| 11.4 COMPENSATION CLEAR ·····                        |          |

| 11.5 DATA INPUT                                      | ••••• 64 |

| 11.6 EXECUTION OF EXTERNAL COMPENSATION ·····        |          |

| 11.7 INTERRUPTION DURIING COMPENSATION               |          |

| 11.8 OFFSET VALUE ±MAX. REACH·····                   |          |

| 12. M-NET INTERFACE ······                           |          |

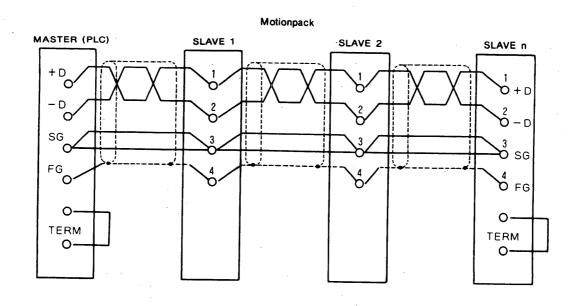

| 12.1 SPECIFICATIONS OF M-NET INTERFACE               |          |

| 12.2 DATA SIGNAL CONNECTION                          |          |

| 12.3 SETTING ·····                                   |          |

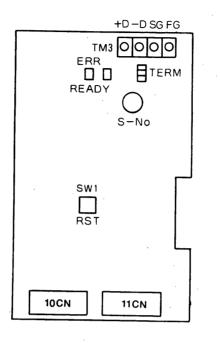

| 12.4 PARTS ARRANGEMENT AND FUNCTIONS                 |          |

| 13. I/O SIGNAL LIST                                  | ••••• 72 |

| 13.1 MAIN CONTROLLER FIXED INPUT SIGNALS             |          |

| 13.2 MAIN CONTROLLER FIXED OUTPUT SIGNALS            |          |

| 13.3 BUILT-IN SEQUENCER INPUT SIGNALS                |          |

|                                                      |          |

## CONTENTS (Cont'd)

#### Page

# INDEX

|              | Subject                                                                                                                                                                          | Chapte                                 | er Secti                                   | ion No.                                 | Page                         |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------------|-----------------------------------------|------------------------------|

| Α            | ABSOLUTE VALUE COMPENSATION ······ADDRESS MAP ···································                                                                                                | ••• 3                                  | 3                                          | .3                                      | • 10                         |

| В            | BEFORE USING BUILT-IN SEQUENCERBUILT-IN SEQUENCER INPUT SIGNALSBUILT-IN SEQUENCER INSTRUCTIONSBUILT-IN SEQUENCER OUTPUT SIGNALSBUILT-IN SEQUENCER SYSTEM CONFIGURATION           | ···· 3<br>···· 13<br>···· 4<br>···· 13 | ····· 1<br>····· 1                         | 3.3                                     | · 8<br>· 78<br>· 16<br>· 79  |

| C            | CHECKING LOGIC<br>CHECKING LOGIC PROGRAM SYNTAX<br>COMPENSATION CLEAR<br>CONNECTING TO PROM WRITER<br>CONNECTION WITH PERSONAL COMPUTER                                          | ··· 7<br>··· 7<br>··· 11               | ····· 7.<br>···· 1                         | .1<br>1.4<br>.1                         | · 50<br>· 50<br>· 64<br>· 51 |

|              | CONNECTION WITH PERSONAL COMPUTER Counter Assignment Table CONTROL INSTRUCTIONS                                                                                                  | ·· A-3<br>·· 13                        | •••••• 1:                                  | 3.5.2 • • • •                           | • 90<br>• 81                 |

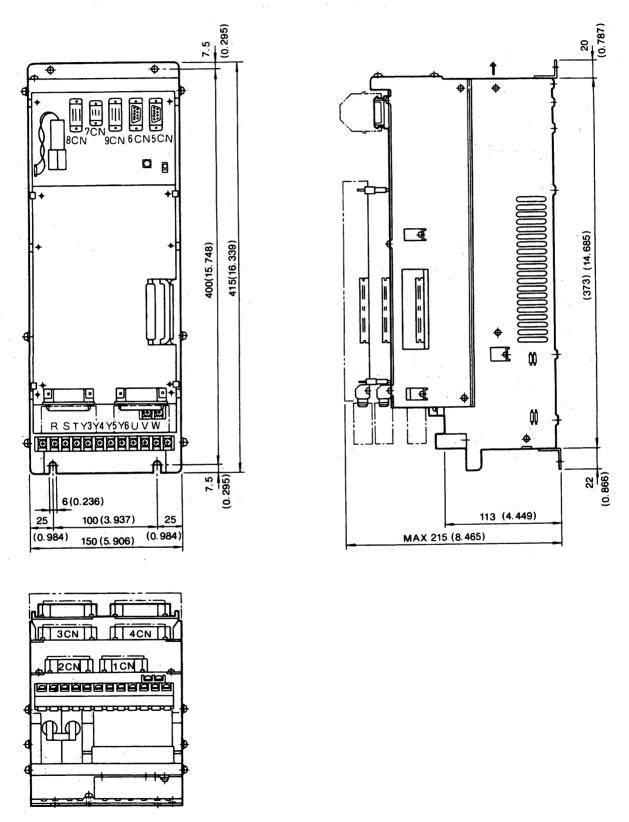

| D            | DATA INPUT<br>DATA SIGNAL CONNECTION<br>DIMENSIONS in mm (in inches)                                                                                                             | ·· 11<br>·· 12                         | ····· 1                                    | 1.5 ·····<br>2.2 ·····                  | • 64<br>• 67                 |

| E            | ENVIRONMENT<br>EXPLANATIONS OF BUILT-IN SEQUENCER INSTRUCTIONS<br>EXTERNAL COMPENSATION<br>EXTERNAL DATA SETTING AND<br>INTERNAL DATA READ-OUT<br>EXTERNAL DATA SETTING FUNCTION | ··A-1<br>·· 5<br>·· 11<br>·· 10        | ·<br>· · · · · · · · · · · · · · · · · · · | ••••••                                  | · 87<br>· 18<br>· 63<br>· 56 |

|              | EXTERNAL DATA SETTING SEQUENCE ······<br>EXTERNAL OF EXTERNAL COMPENSATION ·····                                                                                                 | •• 10                                  | 10                                         | ).3                                     | · 59                         |

| F            | FIXED I/O SIGNALS<br>FIXED INPUT SIGNALS<br>FIXED OUTPUT SIGNALS<br>FORMAT OF LIST FORMAT FILE<br>FORMAT OF ORIGINAL LADDER FILE                                                 | ·· 9<br>·· 9 ·<br>·· 9 ·               | 9.<br>                                     | 1 · · · · · · · · · · · · · · · · · · · | · 53<br>· 53<br>· 55<br>· 47 |

| <b>1</b><br> | I/O MAP (INTERNALLY-FIXED ADDRESS)<br>I/O SIGNAL LIST<br>I/O SIGNAL SPECIFICATIONS<br>INCREMENTAL VALUE COMPENSATION<br>INTERNAL DATA READ-OUT SEQUENCE                          | ·· 10··<br>·· 13<br>·· 13 ·<br>·· 11 · | ····· 10<br>····· 13<br>···· 11            |                                         | 57<br>72<br>82<br>64         |

|              | INTERRUPTION DURING COMPENSATION                                                                                                                                                 | • 11 •                                 | 11                                         | .7                                      | 65                           |

| L            | LOGIC PROGRAM EDITING                                                                                                                                                            | •• 6 •                                 | ••••• 6.1                                  | · · · · · · · · · · ·                   | 46<br>46                     |

# INDEX (Cont'd)

|          | Subject                                                                                                                                                     | Chapter                                          | Section No.                                         | Page                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------|-------------------------------------|

| <b>M</b> | MAIN CONTROLLER FIXED INPUT SIGNALS<br>MAIN CONTROLLER FIXED OUTPUT SIGNALS<br>M-NET INTERFACE<br>MODEL 1 PARAMETER SETTING<br>Motionpack FD SERIES MODEL 1 | ··· 13 ···<br>··· 12 ···<br>··· 1 ··<br>··· 1 ·· | ···· 13.2 ····                                      | ···· 75<br>··· 66<br>··· 3<br>··· 1 |

| 0        | OFFSET VALUE MAX. REACH ······<br>OPERATION PROCEDURES ······<br>OUTLINE OF BUILT-IN SEQUENCER ·····                                                        | ···A-2 ·                                         | • • • • • • • • • • • • • •                         | ••• 88                              |

| Ρ        | PARTS ARRANGEMENT AND FUNCTIONS<br>PERIPHERAL DEVICES<br>PERSONAL PROGRAM LIST<br>PROCEDURE FOR STORING LOGIC PROGRAM INTO ROM                              | ···· 2 ···<br>···· A-4 ·                         | •••• 2.1 ••••                                       | ···· 6<br>··· 91                    |

| R        | REGISTER INSTRUCTIONS<br>RELATIONS BETWEEN I/O SIGNALS AND ADDRESS<br>RELAY INSTRUCTIONS                                                                    | 3                                                | •••• 3.4 •••••                                      | ••• 15                              |

| S        | SETTING<br>SIGNALS<br>SPECIFICATIONS<br>SPECIFICATIONS OF COMPENSATION DATA<br>SPECIFICATIONS OF M-NET INTERFACE                                            | ···· 10 ···<br>··· 2 ···<br>··· 11 ···           | 10.1 · · · · · 2.2 · · · · · 11.1 · · · ·           | ···· 56<br>···· 7<br>···· 63        |

|          | SPECIFICATIONS OF MODEL 1 ······<br>STORING LOGIC PROGRAM IN ROM ······<br>SYSTEM CONFIGURATION ·····                                                       | 8 .                                              |                                                     | ••• 51                              |

| Т        | TECHNICAL TERMS<br>TIMER AND COUNTER INSTRUCTIONS<br>TIMER AND COUNTER LIST<br>Timer Assignment Table                                                       | ···· 3 ···<br>··· 5 ···                          | ····· 3.1 ·····<br>···· 5.3 ·····<br>···· 13.5 ···· | ···· 8<br>···· 23<br>···· 80        |

# 1. Motionpack FD SERIES MODEL 1

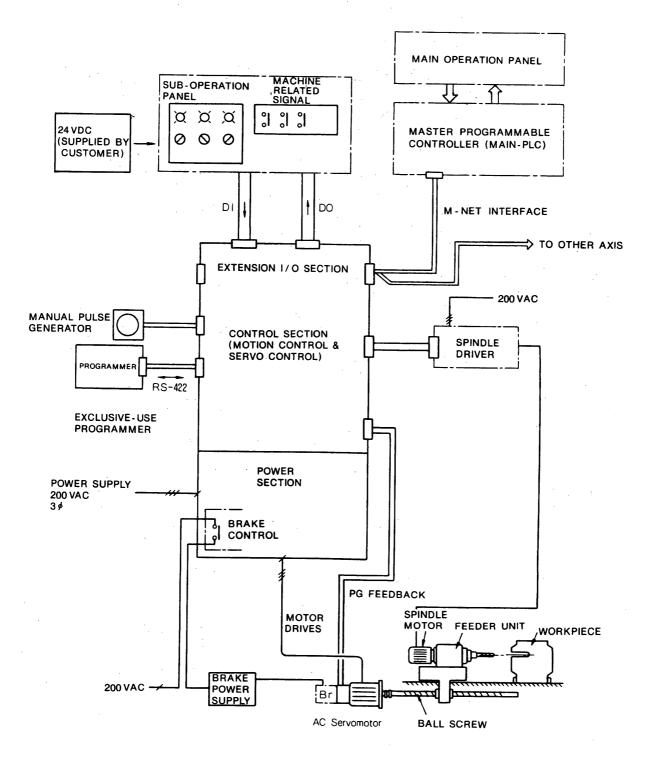

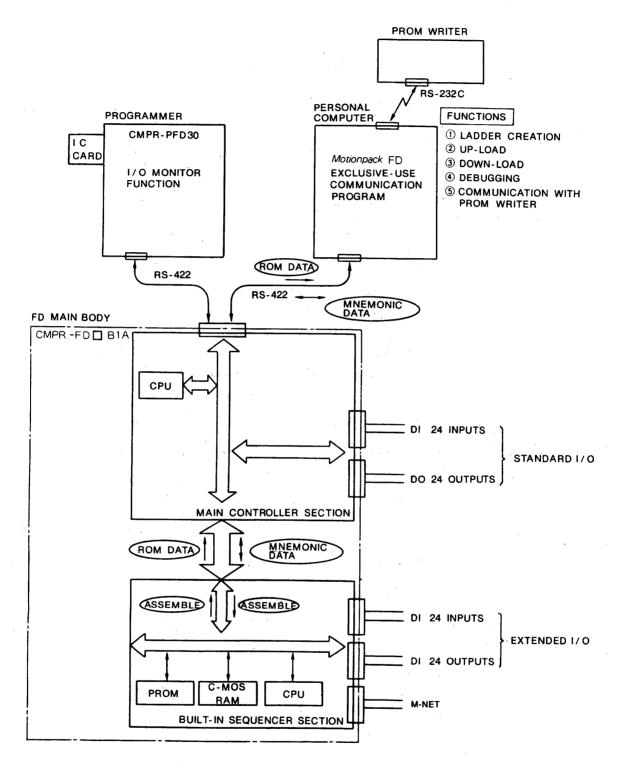

# **1.1 SYSTEM CONFIGURATION**

### 1.2 SPECIFICATIONS OF MODEL 1

The following table shows the functions that can be used for the model 1, compared with those of the basic system.

| Item                                     | Basic System (Model 0)                         | Extension System (Model 1)                                  |

|------------------------------------------|------------------------------------------------|-------------------------------------------------------------|

| Туре                                     | CMPR-FD 🗌 B0 🗌                                 | CMPR-FD 🗌 B1 🗌                                              |

| Hardware                                 | Basic section                                  | Basic section + PLC board                                   |

| Built-in PLC                             | Not available                                  | Available                                                   |

| Solid Tap                                | Not available                                  | Not available                                               |

| No. of Programs                          | Up to 16                                       | Up to 32                                                    |

| No. of Program Blocks                    | Up to 1000                                     | Up to 1000                                                  |

| Standard I/O                             | I/O = 24/24                                    | I/O = 24/24                                                 |

| Extended I/O                             | Not available                                  | I/O = 24/24                                                 |

| M-NET Interface                          | Not available                                  | Used (Y-mode, T-mode)                                       |

| Spindle Reference                        | Analog reference ±10 V<br>S-reference possible | Analog reference $\pm 10 \text{ V}$<br>S-reference possible |

| No. of Indirect Registers                | R01 to R99                                     | R01 to R99                                                  |

| Indirect Register Data<br>Setting Method | Programmer                                     | Programmer<br>External Data Setting                         |

| External Data Setting                    | Not available                                  | Available                                                   |

| Coordinate Compensation                  | Provided (T1 to T9)                            | Provided (T1 to T9)                                         |

| External Compensation                    | Not available                                  | Available                                                   |

Table 1.2 Specifications of Model 1

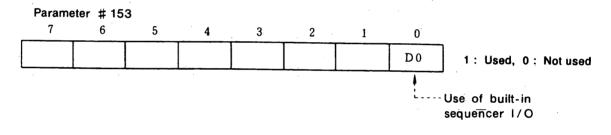

# 1.3 MODEL 1 PARAMETER SETTING

Set the model 1 the following parameters which are added to the basic system, if necessary.

| Pr. No. | Name (Range/Unit) | Change |                              | Descr         | iption                                               |  |

|---------|-------------------|--------|------------------------------|---------------|------------------------------------------------------|--|

|         |                   |        | $\Pr{150} = \square$         | Baud Rate S   | Setting                                              |  |

|         |                   |        |                              | Set Value     | Baud Rate                                            |  |

|         |                   |        |                              | 0             | 4.8 kbps                                             |  |

|         |                   |        |                              | 1             | 9.6 kbps                                             |  |

|         |                   |        |                              | 2             | 19.2 kbps                                            |  |

|         |                   |        |                              | 3             | 38.4 kbps                                            |  |

|         |                   |        |                              |               |                                                      |  |

|         |                   | ÷      |                              | M-NET Inte    | rface Setting                                        |  |

| D 450   | M-NET Interface   |        |                              | Set Value     | M-NET                                                |  |

| Pr150   | Setting           | Р      |                              | 0             | Not provided                                         |  |

|         |                   |        |                              | 1             | T-type                                               |  |

|         |                   |        |                              | 2             | Y-type                                               |  |

|         |                   |        |                              |               |                                                      |  |

|         |                   |        | EXAMPLE 1) P<br>EXAMPLE 2) P | r150 = 21 : Y | 1-NET not provi<br>7-type provided<br>1-NET Baud rat |  |

Table 1.3 Additional Parameters for Model 1

# 1.3 MODEL 1 PARAMETER SETTING (Cont'd)

| Pr. No. | Name (Range/Unit)                                                                                                                                                                                                                                                                                                                                           | Change | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Transmission<br>Points Setting<br>RSW1                                                                                                                                                                                                                                                                                                                      | Р      | The following three conditions are set to Pr151.<br>(1) No. of discrete input data transmission points (RSW1)<br>(2) No. of discrete output data transmission points (RSW2)<br>(3) No. of register data transmission points (RSW3)<br>Pr151 is expressed in 5-decimal digit.<br>Pr151 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Pr151   | RSW1         No.       Dl<br>(Point)         0       0         1       8         2       16         3       24         4       32         5       40         6       48         7       56         8       64         9       72         10       80         11       88         12       96         13       104         14       120         15       128 | DO No  | Decomposition       No.       RI       RO       No. of Connectable         Slave Stations $2 3 4 5 6 7$ $1 2 3 4 5 6 7$ $1 2 3 4 5 6 7$ I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I </td |

Table 1.3 Additional Parameters for Model 1 (Cont'd)

| Pr. No. | Name (Range/Unit)                                  | Change | Description                                                                                                                                                    |

|---------|----------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pr152   | Keep-memory<br>Heading Address<br>(4800 to 5999/ ) | P      | The heading address of keep-memory on the address map<br>is set to Pr152.<br>EXAMPLE 1) Pr152 = 5400 :<br>#5400 to #5999 are the keep memory (keep registers). |

| Pr153   | Built-in Sequencer<br>Provided/Not<br>Provided     | Р      | Whether the built-in sequencer is provided or not is set<br>to Pr153.<br>Pr153 =<br>t 0 : Not provided<br>1 : Provided                                         |

Table 1.3 Additional Parameters for Model 1 (Cont'd)

# 2. OUTLINE OF BUILT-IN SEQUENCER

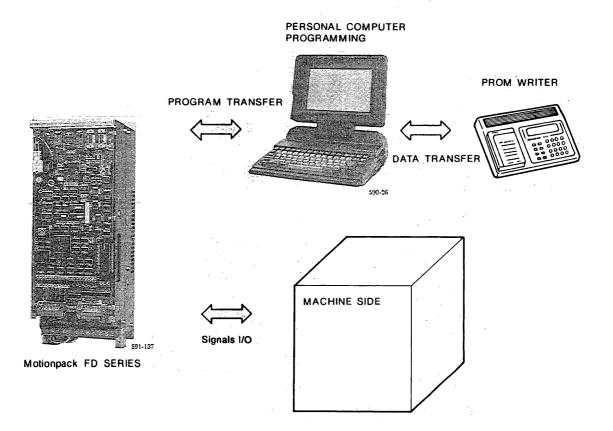

## 2.1 PERIPHERAL DEVICES

### 2.2 SPECIFICATIONS

| Function<br>Control Method |                           | Specifications                                                                                                                                                                   |  |  |  |  |

|----------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                            |                           | Stored program scanning method                                                                                                                                                   |  |  |  |  |

| Scan Time                  |                           | $8 \times N \text{ ms} (N: 1 \text{ or above})$ automatic setting                                                                                                                |  |  |  |  |

| Processing                 | Commands for<br>Relays    | 1.5 μs/step                                                                                                                                                                      |  |  |  |  |

| Time                       | Commands for<br>Registers | 3 to several hundred $\mu$ s/step                                                                                                                                                |  |  |  |  |

|                            | Commands for<br>Relays    | 11 types                                                                                                                                                                         |  |  |  |  |

|                            | Commands for<br>Control   | 9 types                                                                                                                                                                          |  |  |  |  |

| Types of<br>Commands       | Commands for<br>Timer     | 2 types                                                                                                                                                                          |  |  |  |  |

|                            | Commands for<br>Counter   | 2 types                                                                                                                                                                          |  |  |  |  |

|                            | Commands for<br>Register  | 46 types                                                                                                                                                                         |  |  |  |  |

| Sequence Capacity          |                           | 30 kbytes, approx. 7000 steps                                                                                                                                                    |  |  |  |  |

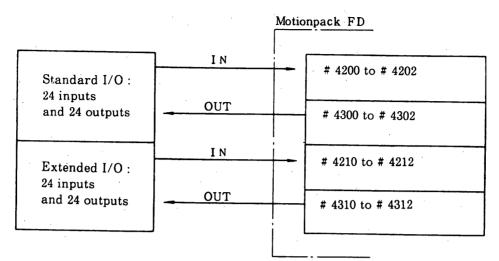

| Number of I/O Points       |                           | Input: 48 points (standard 24 points, extended 24 points)<br>Output: 48 points (standard 24 points, extended 24 points)<br>128 points each for I/O when M-NET interface is used. |  |  |  |  |

|                            | Timer                     | 100 timers (#4600 to #4699)                                                                                                                                                      |  |  |  |  |

|                            | Counter                   | 100 counters (#4700 to #4799)                                                                                                                                                    |  |  |  |  |

| Internal                   | Internal Relay            | Up to 9600 points (#4800 to #5999)*                                                                                                                                              |  |  |  |  |

| Memory                     | Internal Register         | Up to 1200 registers (#4800 to #5999)*                                                                                                                                           |  |  |  |  |

|                            | Keep-memory               | Internal relays or internal register area can be set to holding hocked up memory.                                                                                                |  |  |  |  |

| Programming                |                           | Transferred to built-in sequencer after programming by personal computer.                                                                                                        |  |  |  |  |

### Table 2.1 Specifications of Built-In Sequencer

\* #4800 to #5999 can only be used as internal relays or internal registers.

# 3. BEFORE USING BUILT-IN SEQUENCER

#### 3.1 TECHNICAL TERMS

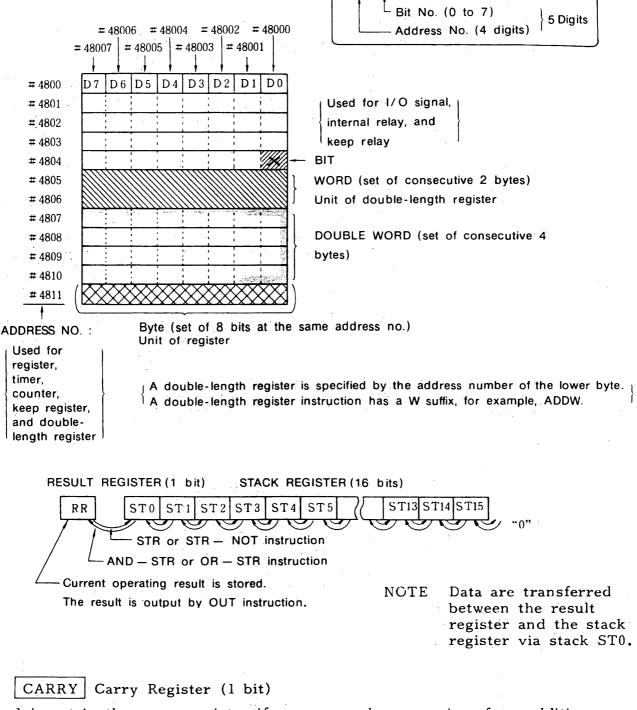

**#48000**

l is set in the carry register if a carry or borrow arises from addition or subtraction. The carry register cannot be incorporated in the stack register. Therefore, the status of the previous carry cannot be stored.

Use the carry register to prevent losing carry information.

# 3.2 BUILT-IN SEQUENCER SYSTEM CONFIGURATION

NOTE: Standard I/O data are taken in by the main controller section and transmitted to the built-in sequencer section.

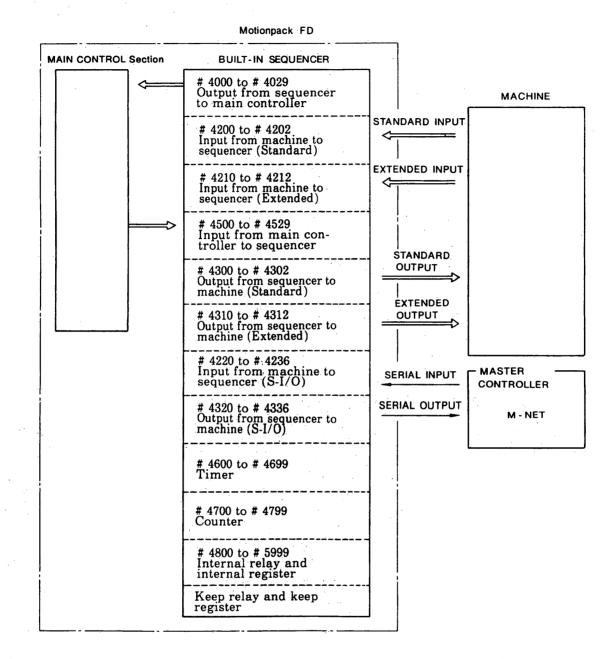

#### 3.3 ADDRESS MAP

Keep memory: This is a battery-backed up memory in which data are kept after power is turned off. Set timer and counter constants in this area. The range of keep memory is determined with a parameter. Set the beginning address of keep memory to parameter # 152. (Example) When 5400 is set for parameter Pr152: #5400 to #5999 are assigned to keep memory or keep register.

Relay, Register: The relay and register areas in the built-in sequencer are used for both relays and registers. Determine the relay and register areas upon use.

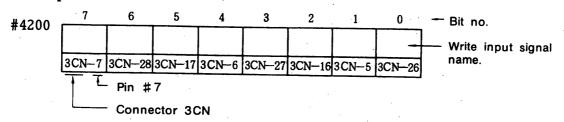

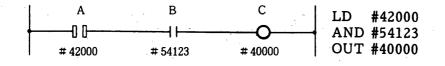

- (1) Addresses for input signals from machine (#4200 to #4202: Standard input signal, #4210 to 4210: Extended input signal) These addresses are assigned to input signals from push buttons and limit switches on the machine operation panel and distribution board. Each signal is specified by a set of an address number and a bit number (#EXERTED). This assignment must be performed by the user.

- (a) One bit of address #4200 corresponds to one input signal.

- (b) The actual address number and bit number are determined by which pin of which I/O connector the input signal is connected to. (Example)

For details, see Section 13 "I/O SIGNAL LIST".

(c) The input signal at address #4200 is represented by the following symbols:

| 00           | <u>1</u> 8   |

|--------------|--------------|

| #42 EEEE     | #42 [][]][]  |

| (NO Contact) | (NC Contact) |

- (d) This address area can be used by a register type command using address numbers only.

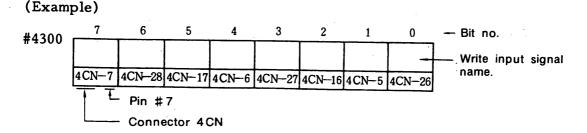

- (2) Addresses for output signals to machine (#4300 to #4302: Standard output signal, #4310 to #4312: Extended output signal)

These addresses are assigned to output signals to lamps and solenoids on the machine operation panel and distribution board. Each signal is specified by a set of an address number and a bit number (# CENTER). This assignment must be performed by the user.

- (a) One bit of address #4300 corresponds to one output signal.

- (b) The actual address number and bit number are determined by which pin of which connector on the I/O board the output signal is connected to.

For details, see Section 13 "I/O SIGNAL LIST".

#### 3.3 ADDRESS MAP (Cont'd)

: / -

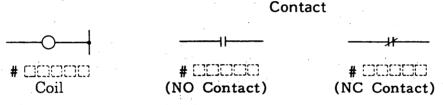

(c) The output signal at address #4300 is represented by the following symbols:

Contact

| ©       |              | <u>-</u>                   |

|---------|--------------|----------------------------|

| #43 EEE | #43 []][][]  | #43 [][[]]<br>(NC Contact) |

| Con     | (NO Contact) | (NC Contact)               |

- (d) This address area can be used by a register instruction by using address numbers only.

- (3) Addresses for input signals from main controller (#4500 to #4529) Seen from the main controller, these addresses are for output signals from the main controller to the built-in sequencer.

(Example) Address No. + bit No. assigned to M-BCD signal

(a) One bit of address #4500 corresponds to one input signal. For details, see Section 13 "I/O SIGNAL LIST".

(Example)

|       | 7      | -6   | 5   | 4   | . 3  | 2.  | 1    | ··· 0 | - Bit no. |

|-------|--------|------|-----|-----|------|-----|------|-------|-----------|

| #4500 | EP ALM | G 34 | OFM | OFR | INCD | STL | SALM | MRDY  |           |

(b) The input signal at address #4500 is represented by the following symbols:

|              | <u>}</u> t   |

|--------------|--------------|

| #45 []][]]   | #45 [][][]   |

| (NO Contact) | (NC Contact) |

- (c) This address area can be used by a register instruction if by using address numbers only.

- (4) Addresses for output signals to main controller (#4000 to #4029)

Seen from the main controller, these addresses are for input signals from the built-in sequencer to the main controller.

(Example) Address No. + bit No. assigned to EDIT signal

(a) One bit of address #4000 corresponds to one output signal.

| (Exam  | pie)<br>7 | 6        | 5        | 4       | 3      | 2    | <b>1</b> . | 0.   | - Bit no. |

|--------|-----------|----------|----------|---------|--------|------|------------|------|-----------|

| #4000  | ZRN       | -JS      | + J S    | JSPD    | HANDLE | JOG  | PLAY       | EDIT |           |

| For de | tails, se | e Sectio | on 13 "I | /O SIGI | NAL LI | ST". |            | · .  | <b>.</b>  |

(b) The output signal at address #4000 is represented by the following symbols:

Contact

•••

•••

•••

#40 [][]][]

#40 [][][]]

#40 [][][]]

Coil

(NO Contact)

(NC Contact)

- (c) This address area can be used by a register instruction by using address numbers only.

- (5) Addresses for timers (#4600 to #4699)

These addresses are assigned to timers. The addresses are used in timer instructions.

- (a) One address number corresponds to one timer.

- (b) Available timers are listed in the following table:

Table 3.1 Time Unit and Number of Timers

| Address No.    | Number of<br>Timers | Time Unit |

|----------------|---------------------|-----------|

| #4600 to #4619 | 20                  | 8 ms      |

| #4620 to #4649 | 30                  | 50 ms     |

| #4650 to #4679 | 30                  | 100 ms    |

| #4680 to #4689 | 10                  | 1 s       |

| #4690 to #4699 | 10                  | 1 min     |

Value 0 to 255 can be set for each timer.

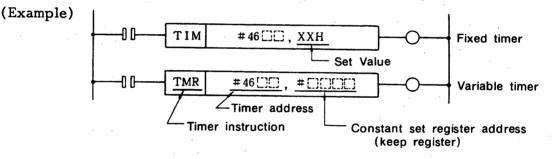

(c) An example of timer symbols is shown in the following:

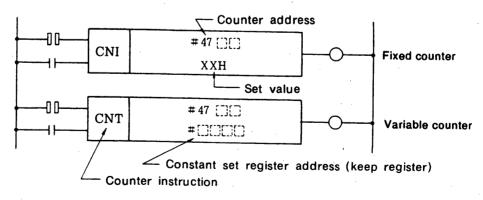

(6) Addresses for counters (#4700 to #4799)

These addresses are assigned to counters. The addresses are used in counter instructions.

- (a) One address number corresponds to one counter.

- (b) An example of counter symbols is shown in the following:

- (Example)

#### 3.3 ADDRESS MAP (Cont'd)

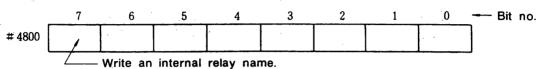

(7) Addresses for internal relays (#4800 to #5999)

These addresses are assigned to internal relays for the built-in sequencer for generating logic programs. Each relay is assigned to a set of an address number and a bit number.

(a) One bit of address #4800 corresponds to one internal relay.

(Example)

(b) An internal relay and the contact are represented by the following symbols:

- (c) This address area can be used by a register instruction by using address numbers only.

- (d) An internal relay assigned in the keep memory area works as a keep relay.

- (8) Addresses for internal registers (#4800 to #5999)

These address numbers are assigned to internal 1 byte (8 bit) register.

(a) One address corresponds to one 1 byte register.

(Example) # 4800 \_\_\_\_\_\_\_\_ Write a register name.

(b) The address number itself is the representation symbol of a register.

- (c) A register assigned in the keep memory works as a keep register.

- (d) A double-length register is specified by the address number of the lower byte.

# 3.4 RELATIONS BETWEEN I/O SIGNALS AND ADDRESS

NOTE Selection of built-in sequencer is set in parameter Pr153. Pr153 (D0) must be set to 1 to use built-in sequencer.

Otherwise, built-in sequencer is impossible to cannot be use.

### 4. BUILT-IN SEQUENCER INSTRUCTIONS

| Re        | alay Instructions                       | Function                  |

|-----------|-----------------------------------------|---------------------------|

| D LD      | #×××××                                  | Load                      |

| 2 LD-NOT  | $\# \times \times \times \times \times$ | NOT                       |

| 3 AND     | #×××××                                  | AND                       |

| AND-NOT   | #×××××                                  | AND-NOT                   |

| 5 OR      | <b>#</b> ×××××                          | OR                        |

| 6 OR-NOT  | #×××××                                  | OR-NOT                    |

| ⑦ STR     | $\# \times \times \times \times \times$ | Store result and load     |

| 8 STR-NOT | #×××××                                  | Store result and load NOT |

| 9 AND-STR |                                         | AND with stored result    |

| 10 OR-STR |                                         | OR with stored result     |

| 1) OUT    | <b>#</b> ×××××                          | Output result to relay    |

#### Table 4.1 Relay Instructions

Table 4.2 Control Instructions

|                | Control Instructions | Function                    |

|----------------|----------------------|-----------------------------|

| 1              | NOP                  | No operation                |

| 2              | MCR                  | Master control relay        |

| 3              | END                  | End of master control relay |

| 4              | RET                  | End of sequence             |

| 5              | RTI                  | Conditional end of sequence |

| 6              | SET                  | Set result                  |

| $\overline{O}$ | RST                  | Clear result                |

| 8              | STC                  | Set carry                   |

| <b>9</b> .     | CLC                  | Clear carry                 |

#### Table 4.3 Timer and Counter Instructions

| • •  | Timer and Counter Instr                                                                    | uctions Function |

|------|--------------------------------------------------------------------------------------------|------------------|

| D TI | $\mathbf{M}  \# \times \times \times \times \times \times \mathbf{H}$                      | Fixed timer      |

| 2 TI | $MR  \texttt{\#} \times \times \times \times, \ \texttt{\#} \triangle \triangle \triangle$ | Variable timer   |

| 3 C  | $\mathbf{NI}  \# \times \times \times \times, \ \times \times \mathbf{H}$                  | Fixed counter    |

| 4) C | $NT  \# \times \times \times \times, \ \# \triangle \triangle \triangle$                   | Variable counter |

|                 | Register Instructions                                              | Function                          |

|-----------------|--------------------------------------------------------------------|-----------------------------------|

| ① CMR           | # × × × ×                                                          | Invert byte register              |

| 2 CMRW          | # × × × ×                                                          | Invert word register              |

| 3 ADI           | # × × × × , × × H                                                  | Add binary constant               |

| 4 ADD           | $\# \times \times \times \times, \# \triangle \triangle \triangle$ | Add byte register                 |

| 5 ADC           | $\# \times \times \times \times, \# \triangle \triangle \triangle$ | Add byte register with carry      |

| 6 ADDW          | $\# \times \times \times \times, \# \triangle \triangle \triangle$ | Add word register                 |

| ⑦ ADCW          | $\# \times \times \times \times, \# \triangle \triangle \triangle$ | Add word register with carry      |

| 8 DAD           | $\# \times \times \times \times, \# \triangle \triangle \triangle$ | Add 2-digit BCD                   |

| 9 DADS          | # × × × × , # △ △ △ , # 0000                                       | Add any-even-number-of-digit BCD  |

| 10 SBI          | $\# \times \times \times \times, \times \times H$                  | Subtract binary constant          |

| 1 SUB           | $\# \times \times \times \times, \# \triangle \triangle \triangle$ | Subtract byte register            |

| 12 SBB          | $\# \times \times \times \times, \# \triangle \triangle \triangle$ | Subtract byte register with carry |

| <b>(3)</b> SUBW | $\# \times \times \times \times, \# \triangle \triangle \triangle$ | Subtract word register            |

| <b>(4)</b> SBBW | $\# \times \times \times \times, \# \triangle \triangle \triangle$ | Subtract word register with carry |

|                 |      | Register Instructions                                                                                   | Function                                        |

|-----------------|------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| (15)            | DSB  | $\# \times \times \times \times$ , $\# \triangle \triangle \triangle$                                   | Subtract 2-digit BCD                            |

| (6)             | DSBS | # × × × ×, #ΔΔΔΔ, #0000                                                                                 | Subtract any-even-number-of-digits,<br>BCD      |

| $\underline{0}$ | MULW | $\# \times \times \times \times$ , $\# \triangle \triangle \triangle$                                   | Word $*$ byte $\rightarrow$ word .              |

| 18              | MULD | $\# \times \times \times \times$ , $\# \triangle \triangle \triangle$                                   | Word $*$ word $\rightarrow$ double word         |

| 19              | DIVW | $# \times \times \times \times, # \triangle \triangle \triangle$                                        | Word/byte $\rightarrow$ word                    |

| 20              | ANI  | $\# \times \times \times \times, \times \times H$                                                       | Binary constant AND byte register               |

| . 🕘             | ANR  | $\# \times \times \times \times, \# \triangle \triangle \triangle$                                      | Byte register AND byte register                 |

| 22              | ORI  | $# \times \times \times \times, \times \times H$                                                        | Binary constant OR byte register                |

| 23              | ORR  | $\# \times \times \times \times$ , $\# \triangle \triangle \triangle$                                   | Byte register OR byte register                  |

| 2               | SAL  | $# \times \times \times \times, \times \times H$                                                        | Byte register arithmetic left shift             |

| 25              | SAR  | $\# \times \times \times \times, \times \times H$                                                       | Byte register arithmetic right shift            |

| <u>26</u>       | SALW | $# \times \times \times \times, \times \times H$                                                        | Word register arithmetic left shift             |

| <u></u>         | SARW | $\# \times \times \times \times, \times \times H$                                                       | Word register arithmetic right shift            |

|                 | MVI  | $\# \times \times \times \times, \times \times H$                                                       | Byte register, constant transfer                |

|                 | MVIW | $# \times \times \times \times, \times \times \times \times H$                                          | Word register, constant transfer                |

| 30              | MOV  | $\# \times \times \times \times, \# \triangle \triangle \triangle$                                      | Data transfer between byte registers            |

| 31              | MOVS | # × × × ×, #ΔΔΔΔ, #0000                                                                                 | Data transfer between two sets of registers     |

| 32              | DST  | $# \times \times \times \times$ , $\# \triangle \triangle \triangle$ , $\# \times \times H$             | Constant And byte register, and result transfer |

| 33              | DSTW | $# \times \times \times \times$ , $# \triangle \triangle \triangle$ , $# \times \times \times \times H$ | Constant AND word register, and result transfer |

|                 | DIN  | $\# \times \times \times \times$ , $\# \triangle \triangle \triangle$ , $\# \times \times H$            | Byte register data selection                    |

|                 | DEC  | $# \times \times \times \times \times H$                                                                | Unconditional data match detection              |

| 36              | C01  | $# \times \times \times \times, \times \times H$                                                        | Data match detection                            |

| 37              | COR  | $\# \times \times \times \times, \# \triangle \triangle \triangle$                                      | Byte register contents match detection          |

| 38              | CORW | $\# \times \times \times \times, \# \triangle \triangle \triangle$                                      | Word register contents match detection          |

| 39              | СМР  | $# \times \times \times \times, \times \times H$                                                        | Unconditional data comparison                   |

| 40              | CPI  | $# \times \times \times \times, \times \times H$                                                        | Data comparison                                 |

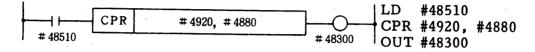

| (1)             | CPR  | $\# \times \times \times \times, \# \triangle \triangle \triangle$                                      | Byte register contents comparison               |

| 42              | CPRW | $\# \times \times \times \times, \# \triangle \triangle \triangle$                                      | Word register contents comparison               |

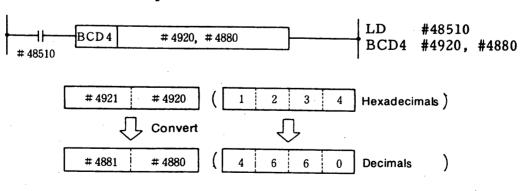

| 43              | BCD4 | $\# \times \times \times \times, \# \triangle \triangle \triangle$                                      | Conversion from binary to 4-digit BCD           |

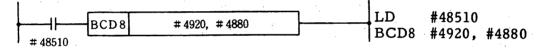

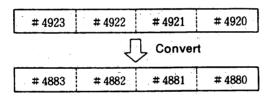

| 44              | BCD8 | $# \times \times \times \times, # \triangle \triangle \triangle$                                        | Conversion from binary to 8-digit BCD           |

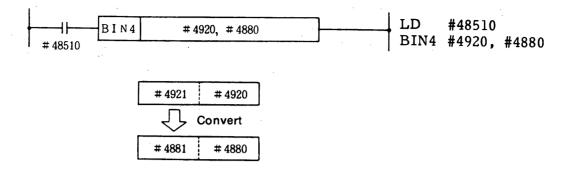

| 45              | BIN4 | $\# \times \times \times \times, \# \triangle \triangle \triangle$                                      | Conversion from 4-digit BCD to binary           |

| <b>46</b>       | BIN8 | $\# \times \times \times \times, \# \triangle \triangle \triangle$                                      | Conversion from 8-digit BCD to binary           |

Table 4.4 Register Instructions (Cont'd)

Table 4.5 Special Instruction

| Special Instruction | Function                   |

|---------------------|----------------------------|

| ① POPR              | Operation error result set |

| ② ERROR             | Download error information |

# 5. EXPLANATIONS OF BUILT-IN SEQUENCER INSTRUCTIONS

#### 5.1 RELAY INSTRUCTIONS

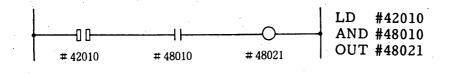

- (1) LD (load) {RR!}

- (a) Format: LD <u>#XXXXX</u>

- Relay Example #42000

- (b) This instruction reads status (1 or 0) of a contact and sets it to RR.

- (c) This instruction is used on normally open (NO) contact.

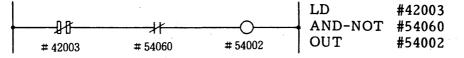

- (2) LD-NOT (load not) {RR}

- (a) Format: LD NOT #XXXXX

- Relay Example #42001 #54120

- (b) This instruction reads status (1 or 0) of an inverted contact and sets it to RR.

- (c) This instruction is used on normally closed (NC) contact.

| Α       | В        | C       | LD-NOT #42001  |  |

|---------|----------|---------|----------------|--|

|         | <u>_</u> |         | AND-NOT #54120 |  |

| # 42001 | # 54120  | # 43001 | OUT #43001     |  |

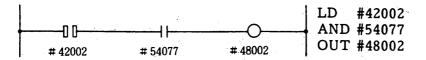

(3) AND {RR}

- (a) Format: AND <u>#XXXXX</u> \_\_\_\_\_ Relay

- (b) This instruction performs AND operation with the contents of RR and a contact (NO contact), then stores the result (1 or 0) to RR.

(4) AND-NOT {RR}

(a) Format: AND-NOT  $\frac{\#XXXXX}{4}$

(b) This instruction performs AND operation with the contents of RR and an inverted contact (NC contact), then stores the result to RR.

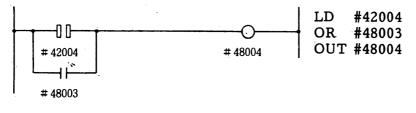

- (5) OR {RR|}

- (a) Format: OR <u>#XXXXX</u> \_\_\_\_\_Relay

- (b) This instruction performs OR operation with the contents of RR and a contact (NO contact), then stores the result to RR.

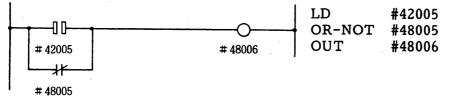

- (6) OR-NOT {RR}

- (a) Format: OR-NOT <u>#XXXXX</u> \_\_\_\_\_\_Relay

- (b) This instruction performs OR operation with the contents of RR and an inverted contact (NC contact), then stores the result to RR.

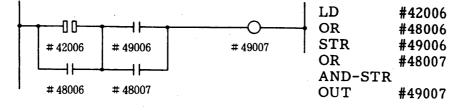

-Relay

(b) This instruction stores the contents of RR then executes the LD instruction.

(c) This instruction is used at NO contact.

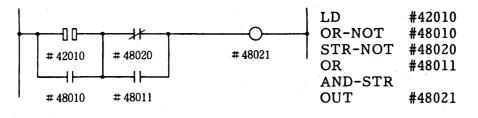

- (8) STR-NOT {RR}

- (a) Format: STR-NOT #XXXXX

-----Relay

#### 5.1 RELAY INSTRUCTIONS (Cont'd)

(b) This instruction stores the contents of RR then executes the LD-NOT instruction.

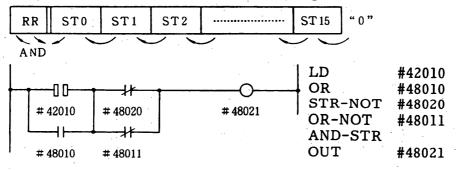

- (9) AND-STR {RR}

- (a) Format: AND-STR

- (b) This instruction performs AND instruction with the contents of RR and stack STO, then stores the result to RR. Contents of the remaining stacks are shifted to the left as shown in the following:

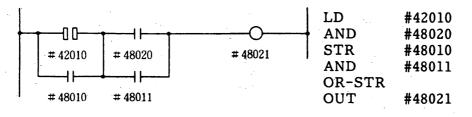

- (10) OR-STR {RR}

- (a) Format: OR-STR

- (b) This instruction performs OR instruction with the contents of RR and stack STO, then stores the result to RR.

(11) OUT {RR**‡**}

(a) Format: OUT #XXXXX

Relay

(b) This instruction writes operation results to relays.

#### **5.2 CONTROL INSTRUCTIONS**

- (1) NOP (No operation) {RR-}

- (a) Format: NOP

- (b) This instruction directs the computer to only proceed to the next step. This instruction does not affect the contents of RR.

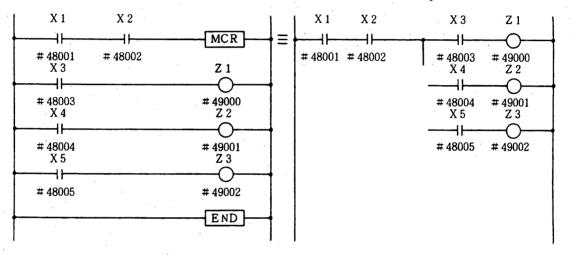

- (2) MCR (Master control) {RR-}

- (a) Format: MCR

- (b) If RR before MCR is 1, this instruction releases the sequence ladder between MCR and EWD is executed.

If RR before MCR is 0, this instruction writes 0 to all relays before END.

| LD | #4800 |

|----|-------|

|    |       |

1

| AND | #48002 |

|-----|--------|

| MCR |        |

If contacts X1 and X2 are off, 0 is output to internal relays, Z1, Z2, and Z3.

| LD - | #48003 |

|------|--------|

| OUT  | #49000 |

| LD   | #48004 |

| OUT  | #49001 |

| LD   | #48005 |

| OUT  | #49002 |

| END  |        |

- (c) Between MCR and END, other MCR and END can be added. (The maximum nesting level is seven.)

- (d) If a timer or counter instruction is included in MCR, the timer or counter is cleared when MCR is off.

- (e) An auto retention circuit can be incorporated in MCR, but the output from the auto retention circuit automatically becomes off (0) when MCR is off.

- (3) END (Master control end) {RR-}

- (a) Format: END

- (b) This instruction indicates the end of master control.

#### 5.2 CONTROL INSTRUCTIONS (Cont'd)

- (4) RET (Return) {RR-}

- (a) Format: RET

- (b) This instruction indicates the end of the sequence program.

- (5) RTI (Return indirect) {RR-}

- (a) Format: RTI

- (b) If RR before the RTI instruction is 1, the computer executes the RET instruction. If RR before the RTI instruction is 0, the next step is executed.

- (6) SET {RR-}

- (a) Format: SET

- (b) This instruction sets RR to 1.

- (7) RST (Reset)  $\{RR = 0\}$

- (a) Format: RST

- (b) This instruction resets RR to 0.

- (8) STC (Set carry) {RR-}

- (a) Format: STC

- (b) This instruction sets the carry to 1.

(9) CLC (Clear carry) {RR-}

- (a) Format: CLC

- (b) This instruction clears carry to 0.

#### **5.3 TIMER AND COUNTER INSTRUCTIONS**

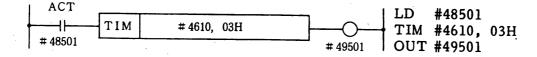

(1) TIM (Fixed timer)  $\{RR \text{ time up} = 1\}$

(a) Format: TIM #XXXX, XXH

Timer set time Timer set address (#4600 to #4699)

- (b) If ACT before the TIM instruction is 1, the timer starts count-up and when the set time has elapsed, the result RR is set to 1. The RR is 0 until the time elapses. If ACT before the TIM instruction is 0, the timer is reset and the result RR is cleared to 0.

- (c) Time can be set in the range of 0 to 255 in decimal number. The instruction must be written in hexadecimals.

- (d) There are five types of timers as listed in the table:

| Address        | Туре                          | Qty |

|----------------|-------------------------------|-----|

| #4600 to #4619 | Set value 1 equals to 8 ms.   | 20  |

| #4620 to #4659 | Set value 1 equals to 50 ms.  | 30  |

| #4660 to #4679 | Set value 1 equals to 100 ms. | 30  |

| #4680 to #4689 | Set value 1 equals to 1 s.    | 10  |

| #4690 to #4699 | Set value 1 equals to 1 min.  | 10  |

NOTE 1. Do not use duplicated address for fixed and variable timers.

- 2. Time error is the time set unit of the timer. Use a small-scale timer when precision is required.

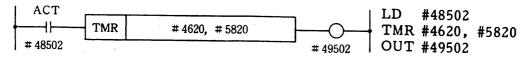

- (2) TMR (Variable timer) {RR time up = 1}

- (a) Format: TMR #XXXX, #XXXX

Timer constant set register address Timer address (#4600 to #4699)

- (b) If ACT before the TMR instruction is 1, the timer starts count-up and when the set time has elapsed, the result RR is set to 1. The RR is 0 until the time elapses. If ACT before the TMR instruction is 0, the timer is reset and the result RR is cleared to 0.

- (c) Time can be set by a decimal number from 0 to 255.

- (d) Time address must be set in the keep memory area.

- (e) Similar to the TIM instruction, five types of timers are available. The duplicated timer address cannot be shared by the TIM and TMR instructions.

#### 5.3 TIMER AND COUNTER INSTRUCTIONS (Cont'd)

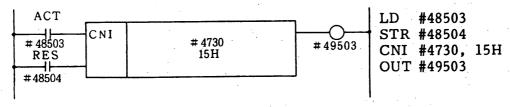

(3) CNI (Fixed down counter) {RR count up = 1}

- (a) Format: LD #XXXXX + Counter input STR #XXXXX + Reset input CNI <u>#XXXX, XXH</u> COUNTER preset value Counter address (#4700 to #4799)

- (b) If the reset input (RES) is 1, the counter is preset and RR is reset to 0. Count-down is started when the counter input (ACT) rises from 0 to 1. When the count becomes to 0, RR is set to 1. After that, if ACT changes from 1 to 0, RR is reset to 0.

After the count is reduced to 0, if ACT changes from 0 to 1 before RES goes to 1, the counter is preset from 0 to 255.

(c) Counter preset value range is from 0 to 255 (decimals). The instruction must be written in hexadecimals.

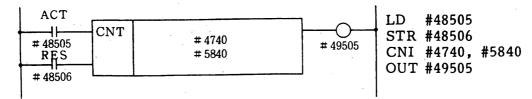

- (4) CNT (Variable down counter) {RR count up = 1}

- (a) Format: LD #XXXXX + Counter input STR #XXXXX + Reset input CNT #XXXX, XXXX

L---- Counter constant set register address ----- Counter address (#4700 to #4799)

- (b) If the reset input (RES) is 1, the counter is preset and RR is reset to 0. Count-down is started when the counter input (ACT) rises from 0 to 1. When the count becomes to 0, RR is set to 1. After that, if ACT changes from 1 to 0, RR is reset to 0.

- After the count is reduced to 0, if ACT changes from 0 to 1 before RES goes to 1, the counter is preset from 0 to 255.

- (c) Counter preset value range is from 0 to 255 (decimals).

- (d) Counter constant set register address must be selected in the keep memory area.

- (e) The duplicated counter address cannot be shared by the CNI and CNT instructions.

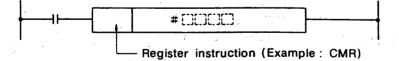

#### 5.4 REGISTER INSTRUCTIONS

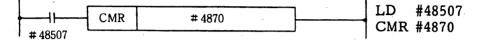

- (1) CMR (Complement register) {RR-}

- (a) Format: CMR <u>#XXXX</u>

#### ----- Register address

- (b) If RR immediately before CMR is 1, the contents of the register are inverted. If RR immediately before CMR is 0, the CMR instruction is not executed.

- (c) A contact must be placed before CMR.

(2) CMRW (Complement word register) {RR-}

This instruction is the same as CMR except that the contents of a double-length register are to be inverted.

- (3) ADI (Add immediate) {RR-}

- (a) Format: ADI  $\frac{\#XXXX}{X}$ ,  $\frac{XXH}{X}$

Numeric value (hexadecimals) ——Register address

- (b) If RR immediately before ADI is 1, the numeric value is added to the contents of the register, then the result is stored in the register. This instruction does not affect the contents of RR or CARRY. If RR immediately before ADI is 0, the ADI instruction is not executed.

- (c) A contact must be placed before ADI.

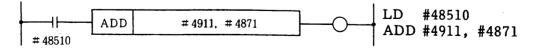

(4) ADD (Add register) {RR-}

- (b) If RR immediately before ADD is 1, the contents of register R1 are added to that of register R2, then the result is stored in register R2.

This instruction does not affect the contents of register R1, RR or CARRY. If RR immediately before ADD is 0, the ADD instruction is not executed.

- (c) A contact must be placed before ADD.

#### 5.4 REGISTER INSTRUCTIONS (Cont'd)

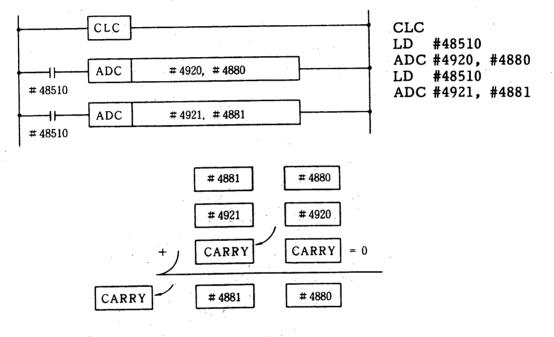

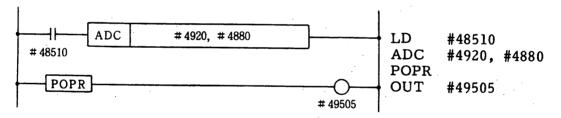

(5) ADC (Add register with carry) {RR:

{RR**‡**, CARRY**‡**}

(a) Format: ADC #XXXX, #XXXX

Augend register (R2) Addend register (R1)

- (b) If RR immediately before ADC is 1, the contents of register R1 and CARRY are added to that of register R2, then the result is stored in register R2. If a carry arises from the addition, RR and CARRY are set to 1. This instruction does not affect the contents of register R1. If RR immediately before ADC is 0, the ADC instruction is not executed.

- (c) A contact must be placed before ADC.

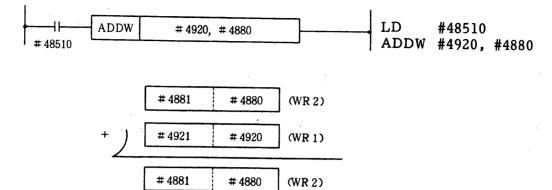

(6) ADDW (Add word register) {RR-}

(a) Format: ADDW #XXXX, #XXXX

Lower byte of double-length register (WR2)

Lower byte of double-length register (WR1)

(b) If RR immediately before ADDW is 1, the contents of double-length register WR1 are added to that of double-length register WR2, then the result is stored in double-length register WR2. This instruction does not affect the contents of double-length register WR1, RR or CARRY.

If RR immediately before ADDW is 0, the ADDW instruction is not executed.

(c) A contact must be placed before ADDW.

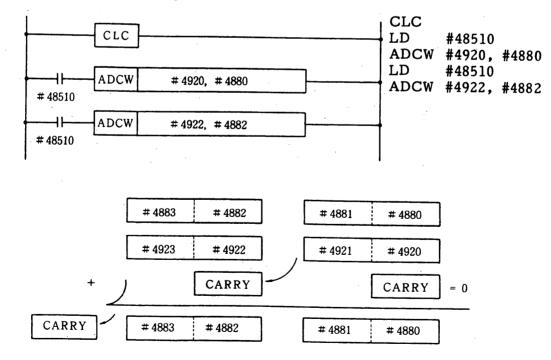

- (7) ADCW (Add word register with carry) {RR1, CARRY1}

- (a) Format: ADCW #XXXX, #XXXX

Lower byte of double-length register (WR2)

----Lower byte of double-length register (WR1)

- (b) If RR immediately before ADCW is 1, the contents of double-length register WR1 and CARRY are added to that of double-length register WR2, then the result is stored in double-length register WR2. If a carry arises from the addition, RR and CARRY are set to 1. This instruction does not affect the contents of double-length register WR1. If RR immediately before ADCW is 0, the ADCW instruction is not executed.

- (c) A contact must be placed before ADCW.

#### 5.4 REGISTER INSTRUCTIONS (Cont'd)

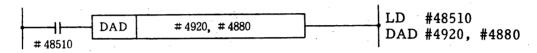

(8) DAD (Decimal add register) {RR‡, CARRY‡}

(a) Format: DAD #XXXX, #XXXX

L\_\_\_\_Augend register (R2) ——Addend register (R1)

(b) If RR immediately before DAD is 1, the contents of register R1 (decimals) are added to that of register R2 (decimals), then the result is stored to register R2.If a carry arises from the addition, RR and CARRY are set to 1.

If RR immediately before DAD is 0, the DAD instruction is not executed.

(c) A contact must be placed before DAD.

Decimal 2-digit Operation

- (9) DADS (Decimal add register string) {RR‡, CARRY‡}

- (a) Format: DADS #XXXX, #XXXX #XXXX

Operation repetition number register (R3) Augend first register (R2) Addend first register (R1)

(b) If RR immediately before DADS is 1, the contents of a specified number of consecutive registers beginning with register R1 are added to the contents of the corresponding number of registers beginning with register R2. The number of additions is set in register R3. The additions are performed on the decimal basis.

If a carry arises in the last register, RR and CARRY are set to 1. If RR immediately before DADS is 0, the DADS instruction is not executed.

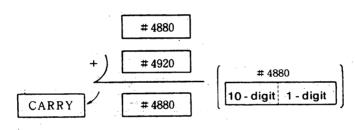

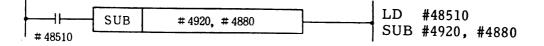

- LD #48510 DADS # 4920, # 4880. # 4820 DADS #4920, #4880, #4820 # 48510 If a content of #4820 is "4" (Decimal 8-digit Operation) # 4883 # 4882 # 4881 #4880 # 4923 # 4922 # 4921 # 4920 CARRY CARRY CARRY CARRY # 4883 # 4882 # 4881 #4880 (10) SBI (Subtract immediate)  $\{RR-\}$ (a) Format: SBI #XXXX, XXH -Numeric value (hexadecimals) Register address (b) If RR immediately before SBI is 1, the numeric value is subtracted from the contents of the register, then the result is stored in the This instruction does not affect the contents of RR or register. CARRY. If RR immediately before SBI is 0, the SBI instruction is not executed. (c) A contact must be placed before SBI. LD #48510 SBI #4880, 20 H SBI #4880, 20H #48510(11) SUB (Subtract register)  $\{RR-\}$ (a) Format: SUB #XXXX, #XXXX

- \_\_\_\_\_ Minuend register (R2) \_\_\_\_\_Subtrahend register (R1)

- (b) If RR immediately before SUB is 1, the contents of register R1 are subtracted from that of register R2, then the result is stored in register R2.This instruction does not affect the contents of RR or CARRY. If RR immediately before SUB is 0, the SUB instruction is disregarded.

- (c) A contact must be placed before SUB.

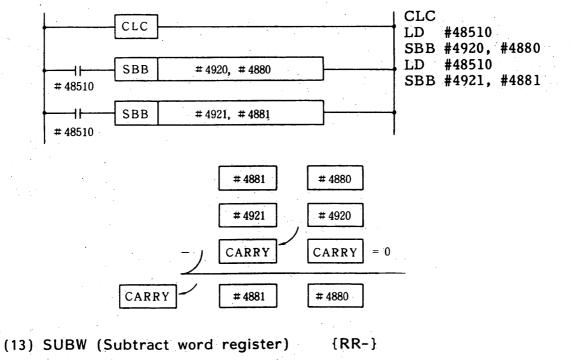

(12) SBB (Subtract register with borrow) {RR, CARRY}

(a) Format: SBB <u>#XXXX</u>, <u>#XXXX</u>

L---- Minuend register (R2) Subtrahend register (R1)

- (b) If RR immediately before SBB is 1, the contents of register R1 and CARRY are subtracted from those of register R2, then the result is stored in register R2. If a borrow arises from the subtraction, RR and CARRY are set to 1. This instruction does not affect the contents of register R1. If RR immediately before SBB is 0, the SBB instruction is not executed.

- (c) A contact must be placed before SBB.

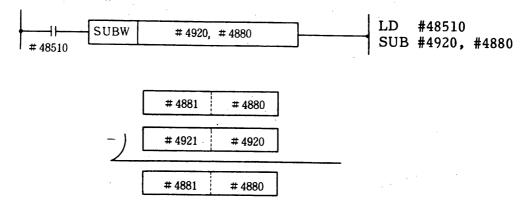

(a) Format: SUBW #XXXX, #XXXX

Lower byte of double-length register (WR2)

-Lower byte of double-length register (WR1)

(b) If RR immediately before SUBW is 1, the contents of double-length register WR1 are subtracted from those of double-length register WR2, then the result is stored in double-length register WR2. This instruction does not affect the contents of RR or CARRY. If RR immediately before SUBW is 0, the SUBW instruction is not executed.

(c) A contact must be placed before SUBW.

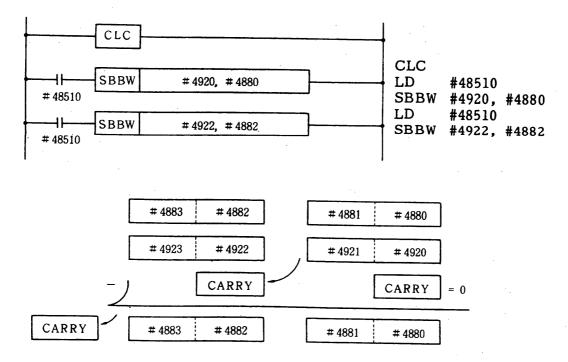

- (14) SBBW (Subtract word register with borrow) {RR1, CARRY1}

- (a) Format: SBBW #XXXX, #XXXX

Lower byte of double-length register (WR2) —Lower byte of double-length register (WR1)

(b) If RR immediately before SBBW is 1, the contents of double-length register WR1 and CARRY are subtracted from those of double-length register WR2, then the result is stored in double-length register WR2.

If a borrow arises from the subtraction, RR and CARRY are set to 1.

If RR immediately before SBBW is 0, the SBBW instruction is not executed.

(c) A contact must be placed before SBBW.

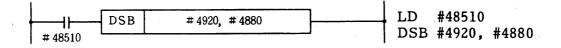

- (15) DSB (Decimal subtract) {RR, CARRY}

- (a) Format: DSB #XXXX, #XXXX

└─── Minuend register (R2) ──── Subtrahend register (R1)

- (b) If RR immediately before DSB is 1, the contents of register R1 (decimals) are subtracted from those of register R2 (decimals), then the result is stored in register R2.If a borrow arises from the subtraction, RR and CARRY are set to 1.If RR immediately before DSB is 0, the DSB instruction is not executed.

- (c) A contact must be placed before DSB.

Decimal 2 - digit Operation

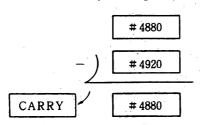

(16) DSBS (Decimal subtract string) {RR‡, CARRY‡}

(a) Format: DSBS #XXXX, #XXXX, #XXXX

Operation repetition number register (R3) Minuend register first address (R2) Subtrahend register first address (R1)

(b) If RR immediately before DSBS is 1, the contents of a specified number of consecutive registers beginning with register R1 are subtracted from the contents of the corresponding number of registers beginning with register R2. The number of subtractions is set in register R3.

If a borrow arises in the last register, RR and CARRY are set to 1. If RR immediately before DSBS is 0, the DSBS instruction is not executed.

- 32 -

(c) A contact must be placed before DSBS.

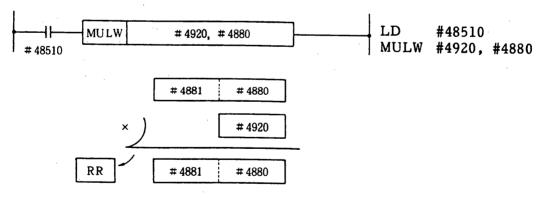

(17) MULW (Multiply word register) {RR}

(a) Format: MULW #XXXX, #XXXX

Lower byte of double-length multiplicand register (WR2) Multiplier register(R1)

(b) If RR immediately before MULW is 1, the contents of double-length register WR2 are multiplied by that of register R1, then the result is stored in double-length register WR2. This instruction does not affect the contents of register R1 or CARRY.

If no overflow results from the multiplication PR is set to 0. If an overflow results from the multiplication PR is set to 0.

If no overflow results from the multiplication, RR is set to 0. If an overflow results from the multiplication, RR is set to 1.

(c) A contact must be placed before MULW.

Signs of the operands are ignored.

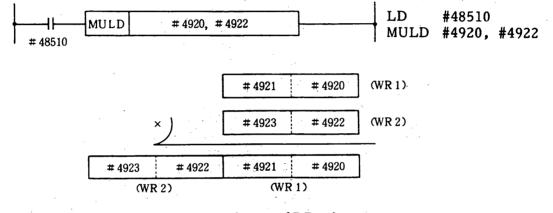

(18) MULD (Multiply word register) {RR-}

(a) Format: MULD <u>#XXXX</u>, <u>#XXXX</u>

Lower byte of double-length register (WR2)

-Lower byte of double-length register (WR1)

- (b) If RR immediately before MULD is 1, the contents of double-length register WR1 are multiplied by that of WR2, then the result is stored using double-length registers WR1 and WR2. This instruction does not affect the contents of RR or CARRY. If RR immediately before MULD is 0, the MULD instruction is not executed.

- (c) A contact must be placed before MULD.

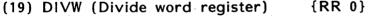

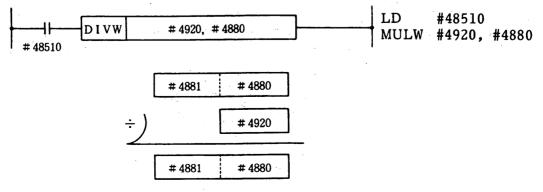

(a) Format: DIVW  $\frac{\#XXXX}{\uparrow}$   $\frac{\#XXXX}{\uparrow}$

Lower byte of divident register (WR2) — Divisor register (R1)

- (b) If RR immediately before DIVW is 1, the contents of double-length register WR2 are divided by that of register R1, then the result is stored in double-length register WR2. Signs of the operands are disregarded. After the division, RR changes to 0. If the divisor is 0, RR remains 1. This instruction does not affect the contents of register R1 or CARRY. If RR immediately before DIVW is 0, the DIVW instruction is not executed.

- (c) A contact must be placed before DIVW.

- 34 -

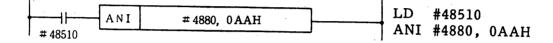

- (20) ANI (And immediate) {RR-}

- (a) Format: ANI <u>#XXXX</u>, <u>XXH</u> <u>L</u> Numeric value (hexadecimals) Register

- (b) If RR immediately before ANI is 1, the numeric value and the contents of the register are ANDed, then the result is stored in the register.

This instruction does not affect the contents of RR or CARRY.

If RR immediately before ANI is 0, the ANI instruction is not executed.

- (c) A contact must be placed before ANI.

|                  | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------------------|----|----|----|----|----|----|----|----|

| Register         | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 1  |

| Numeric<br>Value | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  |

| Result           | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0  |

(21) ANR (Adn register) {RR-}

- (a) Format: ANR <u>#XXXX</u>, <u>#XXXX</u> Operand register (R2) Operand register (R1)

- (b) If RR immediately before ANR is 1, the contents of registers R1 and R2 are ANDed, then the result is stored in register R2. This instruction does not affect the contents of register R1, RR or CARRY.

If RR immediately before ANR is 0, the ANR instruction is not executed.

(c) A contact must be placed before ANR.

ł.

|   |         | ANR | # 4000 # 4000  | ] . | LD  | #48510          |       |

|---|---------|-----|----------------|-----|-----|-----------------|-------|

| I |         | ANK | # 4920, # 4880 |     | ANR | #4920,          | #4880 |

| I | # 48510 |     |                | •   |     | " 1720 <b>,</b> | 11000 |

|               | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---------------|----|----|----|----|----|----|----|----|

| Register (R2) | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 1  |

| Register (R1) | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  |

| Result (R2)   | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1  |

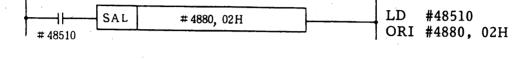

- (22) ORI (Or immediate) {RR-}

- (a) Format: ORI <u>#XXXX</u>, <u>XXH</u> Numeric value (hexadecimals) Register

- (b) If RR immediately before ORI is 1, the numeric value and the contents of the register are ORed, then the result is stored in the register.

This instruction does not affect the contents of RR or CARRY. If RR immediately before ORI is 0, the ORI instruction is not executed.

(c) A contact must be placed before ORI.

|      |     | OR I | # 4880, 55H | ] |   | LD<br>ORI | #48510<br>#4880,55H |

|------|-----|------|-------------|---|---|-----------|---------------------|

| # 48 | 510 |      |             |   | 1 |           | •••                 |

|                  | D7 | D6 | D5 | D4  | D3 | D2 | D1 | D0 |

|------------------|----|----|----|-----|----|----|----|----|

| Register (R2)    | 0  | 0  | 1  | 1   | 0  | 0  | 1  | 1  |

| Numeric<br>Value | 0  | 1  | 0  | 1   | 0  | 1  | 0  | 1  |

| Result           | 0  | 1  | 1  | · 1 | 0  | 1  | 1  | 1  |

<sup>(23)</sup> ORR (Or register)  $\{RR-\}$

(a) Format: ORR #XXXX, #XXXX

United Control of Cont

(b) If RR immediately before ORR is 1, the contents of the registers R1 and R2 are ORed, then the result is stored in the register R2. This instruction does not affect the contents of register R1, RR or CARRY.

If RR immediately before ORR is 0, the ORR instruction is not executed.

(c) A contact must be placed before ORR.

|         |     |                              | 1   | TD  | #48510    |     |

|---------|-----|------------------------------|-----|-----|-----------|-----|

|         | ORR | <b># 4920, <b># 4880</b></b> | · . |     |           |     |

|         | OKK | # 4920, # 4000               |     | ORR | #4920, #4 | 880 |

| # 48510 |     |                              | •   | 1   |           |     |

|               | · D7 | D6  | D5 | - D4 | D3 | D2 | D1 | D0 |

|---------------|------|-----|----|------|----|----|----|----|

| Register (R2) | 0    | 0   | 0  | 1    | 0  | 0  | 0  | 1  |

| Register (R1) | 1    | 0   | 1  | . 0  | 1  | 0  | 1  | 0  |

| Result (R2)   | 1    | ÷ 0 | 1  | 1    | 1  | 0  | 1  | 1  |

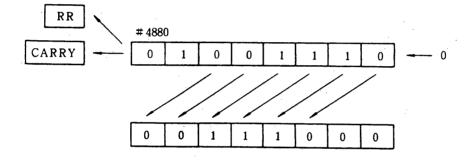

- (24) SAL (Shift left) {RR , CARRY }

(a) Format: SAL <u>#XXXX</u>, <u>XXH</u>

\_\_\_\_\_Numeric value (hexadecimals)

\_\_\_\_\_Register

- (b) If RR immediately before SAL is 1, the contents of the register are shifted to the left for the numeric value. If data "1" overflows from the register after shifting, RR and CARRY are set to 1. If RR immediately before SAL is 0, the SAL instruction is not executed.

- (c) A contact must be placed before SAL.

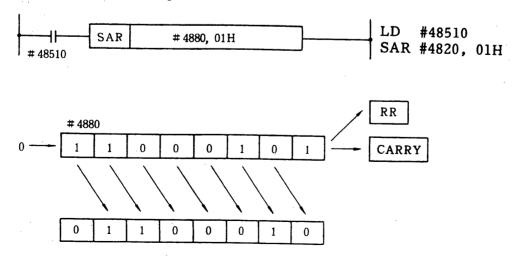

- (25) SAR (Shift right) {RR, CARRY]

- (a) Format: SAR <u>#XXXX</u>, <u>XXH</u> Regist

L---- Numeric value (hexadecimals) Register

- (b) If RR immediately before SAR is 1, the contents of the register are shifted to the right for the numeric value. If data "1" overflows from the register after shifting, RR and CARRY are set to 1. If RR immediately before SAR is 0, the SAR instruction is not executed.

- (c) A contact must be placed before SAR.

- 37 -

{RR, CARRY} (26) SALW (Shift left word register) This instruction is the same as SAL except a double-length register is to be shifted to the left instead of an 8-bit register. {RR, CARRY; } (27) SARW (Shift right word register) This instruction is the same as SAR except a double-length register is to be shifted to the right instead of an 8-bit register. (28) MVI (Move immediate) {RR-} (a) Format: MVI #XXXX, XXH -Numeric value (hexadecimals) - Register (b) If RR immediately before MVI is 1, the numeric value is transferred to the register. This instruction does not affect the contents of RR or CARRY. If RR immediately before MVI is 0, the MVI instruction is not executed. (c) A contact must be placed before MVI. LD #48510 MV Ì # 4880. 0A5H MVI #4880. 0A5H # 48510 (29) MVIW (Move immediated word register)  $\{RR-\}$ This instruction is the same as the MVI instruction except that the constant is to be transferred to a double-length register instead of to an 8-bit register. (30) MOV (Move register)  $\{RR-\}$ (a) Format: MOV #XXXX, #XXXX -Operand register (R2) -Operand register (R1) (b) If RR immediately before MOV is 1, the contents of register R1 are transferred to register R2. This instruction does not affect the contents of register R1, RR or CARRY. The registers (R1 and R2) may be one byte consisting of a set of I/O relays. If RR immediately before MOV is 0, the MOV instruction is not executed. (c) A contact must be placed before MOV. LD #48510

MOV # 4920, # 4880 # 48510 MOV # 4920, # 4880

# (31) MOVS (Move string) {RR-} (a) Format: MOVS <u>#XXXX</u>, <u>#XXXX</u>, <u>#XXXX</u>, <u>#XXXX</u> Operation repetition number register (R3) Operand first register (R2) Operand first Register (R1)

- (b) If RR immediately before MOVS is 1, the contents of a specified number of consecutive registers beginning with register R1 are transferred to the corresponding number of registers beginning with register R2. The number of subtractions is set in register R3. This instruction does not affect the contents of RR, CARRY, or consecutive registers beginning with R1. If RR immediately before MOVS is 0, the MOVS instruction is not executed.

- (c) A contact must be placed before MOVS.

If # 4820 is "04"

| (R 1) | # 4920 | <br># 4880 | (R 2) |

|-------|--------|------------|-------|

|       | # 4921 | <br># 4881 |       |

| i     | # 4922 | <br># 4882 |       |

|       | # 4923 | <br># 4883 |       |

(32) DST (Data store) {RR-}

Operand register (R2) Operand register (R1)

(b) If RR immediately before DST is 1, the numeric value and the contents of register R1 are ANDed, then the result is stored in register R2.

This instruction does not affect the contents of register R1, RR or CARRY.

If RR immediately before DST is 0, the DST instruction is not executed.

(c) A contact must be placed before DST.

| # 48510       | #  | 4920. | # 4880, | 0 FH |    |    |     | LD<br>DST | #48510<br>#4920, #4880, OFH |

|---------------|----|-------|---------|------|----|----|-----|-----------|-----------------------------|

|               | D7 | D6    | D5      | D4   | D3 | D2 | D1  | D0        | A: 1 or 0                   |

| Register (R1) | Α  | A     | A       | A    | A  | A  | A   | A         | A. 1 01 0                   |

| Numeric Value | 0  | 0     | 0       | 0    | 1  | 1  | . 1 | 1         |                             |

| Register (R2) | 0  | 0     | 0       | 0    | A  | Α  | Α   | A         |                             |

(33) DSTW (Data store word register) {RR-}

This instruction is the same as the DST instruction except that this instruction is used for double-length registers (WR1 and WR2) instead of for registers (R1 and R2).

- (34) DIN (Data insert)  $\{RR-\}$

- (a) Format: DIN #XXXX, #XXXX, XXH

-Numeric value (hexadecimals) -Operand register (R2) - Operand register (R1)

(b) If RR immediately before DIN is 1, the inverted numeric data and the contents of register R1 are ANDed, then the result and the contents of register R1 are ORed.

The last result is stored in register R2.

This instruction does not affect the contents of register R1, RR or CARRY.

If RR immediately before DIN is 0, the DIN instruction is disregarded.

(c) A contact must be placed before DIN.

|   |         |     |                     | - |     |           |           |

|---|---------|-----|---------------------|---|-----|-----------|-----------|

|   | ſ       | DIN | # 1000 # 1000 0 FIT |   | LD  | #48510    | 1         |

| 1 |         | DIN | #4920, #4880, 0FH   |   |     | #4920, #4 | 000 050   |

|   | # 48510 |     |                     | - | DIN | #4760, #4 | 000, UFII |

|               | D7 | D6  | D5 | D4 | D3 | D2 | D1 | D0  |

|---------------|----|-----|----|----|----|----|----|-----|

| Register (R1) | А  | A   | Α  | A  | A  | A  | A  | A   |

| Register (R2) | В  | . B | В  | В  | В  | В  | В  | В   |

| Numeric Value | 0  | 0   | 0  | 0  | 1  | 1  | 1  | · 1 |

| Result        | В  | В   | В  | В  | Α  | A  | A  | A   |

A:1 or 0. B:1 or 0.

- (35) DEC (Decode) {RR|}

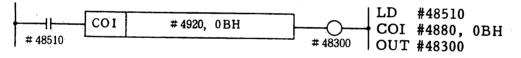

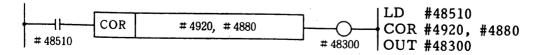

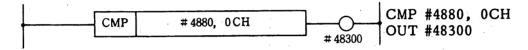

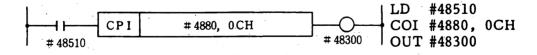

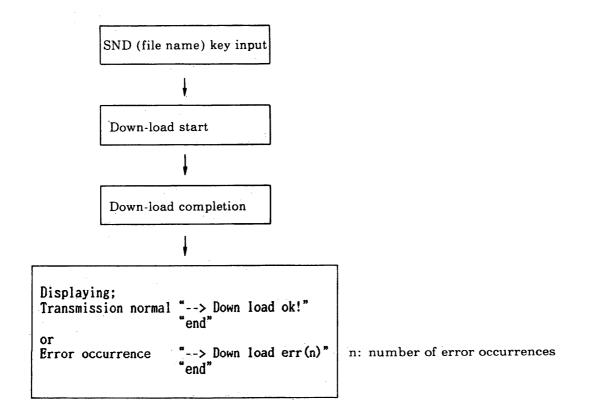

- (a) Format: DEC <u>#XXXX</u>, <u>XXH</u> \_\_\_\_\_Numeric value (hexadecimals) Register